Frog Pacemaker

View CodeESP32-based benchtop pacemaker with adaptive sensing and pacing.

ESP32C++

Overview

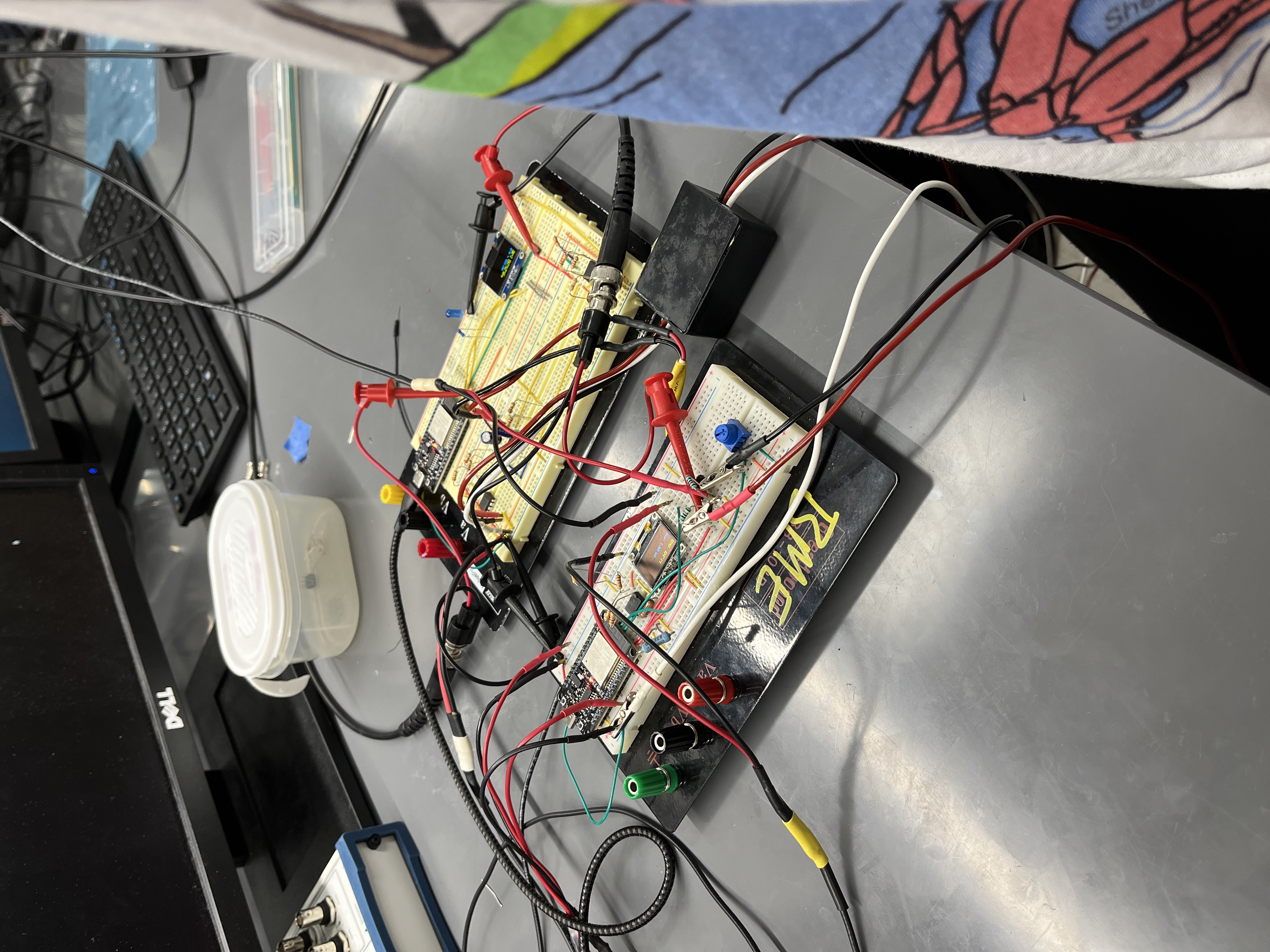

Designed an ESP32-based benchtop pacemaker that senses heart activity and delivers pacing pulses when the heart rate drops below a set threshold. The system features a custom analog front-end for ECG acquisition and runs a real-time firmware using FreeRTOS to ensure precise timing.